안녕하세요 인생리뷰입니다.

오늘은 반도체 회사에 취업하고 싶어하시는 분들을 위해서 가장 중요한 마지막 관문, 바로 전공 면접 예상 및 기출 문제를 가져왔습니다.

(↓↓↓ 아래는 실제 SK 하이닉스 면접 후기입니다. 실제 면접이 어떻게 이루어 졌는지, 제가 받았던 면접 질문은 무엇이었는지 확인해 보세요!)

[반도체 회사 취업 후기] 대기업 취준생을 위한 현직자의 SK하이닉스 취뽀 면접 후기 및 합격 노

안녕하세요 인생리뷰입니다. 저번 주에 삼성전자의 인적성인 GSAT 이 온라인으로 이틀에 걸쳐 종료가 되었다는 소식을 들었는데요. 오늘은 곧 있을 면접에 대비하여, 반도체 회사 면접 후기를

life-review-200822.tistory.com

이제 곧 대기업 면접 시즌인데요, 삼성전자 및 SK하이닉스 뿐만 아니라 다른 반도체 기업에 취업하고자 희망하시는 모든 분들께 도움이 되는 정보였으면 좋겠네요. 아래는 반도체와 관련된 전공 면접 예상 질문입니다.

[반도체 전공 면접 예상 질문]

1. Moore’s Law

마이크로칩의 밀도가 18개월마다 2배로 늘어난다는 법칙.

2. Ge 대신 Si 사용 이유

에너지 밴드갭이 크므로, 높은 온도에서 작동이 가능하다

값이 싸다. SiO2 -> Si

Process가 쉽다. 예) 반도체에서 Thermal oxidation으로도 insulator 가능.

Intrinsic 저항이 크다.

3. 에너지 밴드를 이용한 metal, semiconductor, insulator 비교

Metal은 에너지 밴드들이 겹쳐 있거나, conduct band에 부분적으로 충만 되어 있어서, 전자들이 자유롭게 이동할 수 있다. Insulator는 밴드갭이 커서 valence band에서 conduct band로 transition이 되기 어렵다. Semiconductor는 근본적으로 절연체와 같은 에너지 밴드를 가지지만 밴드갭 에너지가 절연체보다 훨씬 작다. 절연체에 비해 valence band로부터 전도에 기여할 수 잇는 전자수가 반도체에서 열적 또는 광학적 에너지로 크게 증가 될 수 있다. 0K에서 실리콘은 절연체의 고저항을 갖는다.

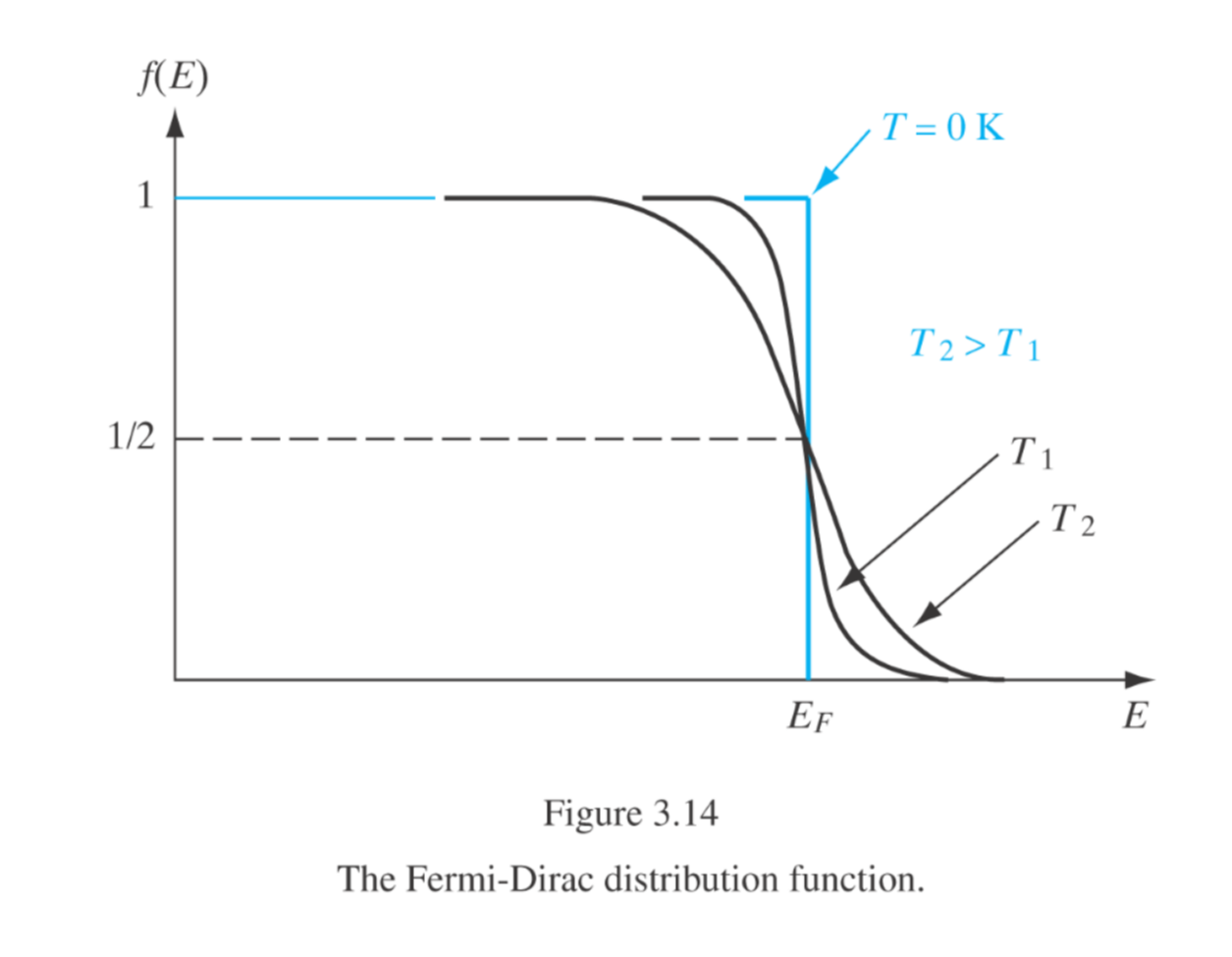

4. Fermi Level이란?

전자가 발견될 확률이 1/2인 에너지 레벨. 도너가 주입되면 Ef(Fermi Level)은 상승하고 억셉터가 주입되면 낮아진다.

5. Pauli 배타율이란?

상호작용이 있는 시스템의 어느 두 개의 전자도 양자수 n, l, m, s 의 같은 짝을 가질 수 없다. 단지 두 개의 전자만이 같은 세기의 양자수 n, l, m을 가질 수 있고, 둘은 반대의 스핀을 가져야 한다.

6. 상태밀도 함수란?

양자상태의 에너지에 관한 분포밀도이다. 작은 구간 내에 존재하는 상태양자수를 그 구간의 에너지 준위로 나눈 값으로 정의하며, 반도체에서 conduct band에 있는 상태밀도는 전자 에너지에 따라 증가하고, valence band에서는 감소한다.

7. Intrinsic Semiconductor에서 온도에 따른 Carrier 농도 변화

Intrinsic 반도체에서는 ni가 온도에 따라 급격하게 증가한다. 즉, 온도의 역수에 선형적으로 증가하는 함수를 보인다.

8. Thermal Equilibrium state와 steady state의 차이점

Thermal Equilibrium state는 외부적 여기가 없고, 실질적인 전하의 이동이 없는 상태를 말한다. (일정한 곳에서 어두운 곳에 있고, 인가된 전계가 없는 시료)

Steady state는 모든 과정이 일정한 상태에 있고 반대되는 과정과 균형이 이루어지는 불평형상태를 말한다. (즉, 일정한 전류가 흐르거나, 일정한 광학적 EHP 생성이 이루어지지만, 이것이 재결합과 균형이 이루어지는 시료)

9. n-type Semiconductor에서 온도에 따른 Carrier 농도 변화

매우 낮은 온도에서는 intrinsic EHP가 거의 존재하지 않는다. 온도가 증가함에 따라 도너의 전자들이 Conduct band로 옮겨지고 약 100K에서 모든 도너 원자가 이온화되는 과정이 발생한다. 이후 ni가 Nd와 비등해 질 때까지(intrinsic carrier 농도가 도너 농도와 비등해 질 때까지) 캐리어 농도는 온도에 영향을 받지 않는다. 온도가 더 증가하면서 진성캐리어 농도는 Nd보다 훨씬 증가하고 ni가 지배하게 된다.

10. Donor와 Accepter의 종류 및 Fermi Level의 변화

도너는 주로 V족 원소로 P, As, Sb 원자로 Conduct band 주위에 에너지 준위가 형성되어 쉽게 전자를 exitation 시킬 수 있으며 페르미 준위는 상승한다.

억셉터는 주로 3족 원소로 B, Al, In 원자로 Valence band 주위에 불순물 준위를 만들어 valence band의 전자를 받아들이고 페르미 준위는 내려간다.

11. Fermi level의 온도의존성

Fermi – Dirac 분포함수는 절대온도 T에서 전자가 점유할 확률을 나타내고 이 확률이 1/2인 에너지 준위를 Fermi level이라고 한다. 이 Fermi level은 온도의 영향은 받지 않고 페르미 함수는 Ef를 중심으로 대칭적은 분포를 나타낸다. 온도가 높아질수록 높은 에너지가 충만해지고, 낮은 에너지는 비어질 확률이 높아질 뿐 페르미 에너지는 변화가 없다.

12. Doping 농도 및 온도에 따른 carrier mobility 변화

Doping 농도가 높아지면 impurity scattering의 영향이 커져 mobility는 감소하게 된다.

온도가 높아지면 격자들의 요동이 커지므로 전자 이동에 방해가 되어 mobility가 감소한다. 반대로 온도가 너무 낮아지면 캐리어의 열적 운동도 낮아지므로 mobility가 감소하게 된다.

13. Band bending 이유

MOS구조에서 전압을 걸어줄 경우, 금속의 에너지 level은 상승하거나 내려간다. 이 때 금속과 반도체의 일함수는 변하지 않으므로 금속의 EFm 은 반도체의 Fermi level 위치보다 올라가거나 내려간다. 이 과정에서 Oxide의 conduct band에 tilt가 생긴다.

14. 온도에 따른 반도체와 금속의 비저항 특성 비교

반도체에서는 온도가 증가함에 따라 저항이 감소하며, 금속에서는 온도가 증가함에 따라 저항이 증가하게 된다. 금속판을 가열할 때에는 가열할 때 가해준 열이 결정격자를 진동시켜 가해준 전자의 이동을 방해하는 역할을 함으로써 결과적으로 저항이 증가하는 효과를 가져온다. 반면 Si wafer를 가열할 때에는 가열할 때 가해준 열이 valence band에 있는 전자가 활성화됨으로써 EHP를 형성함으로써 좀 더 전자가 잘 이동할 수 있는 여건을 조성해 줄 수 있다.

15. Direct/indirect recombination의 비교

GaAs와 같은 Direct 반도체의 경우, valence band로 전자가 재결합확률은 시간당 일정하므로 과잉 캐리어의 감쇠가 지수함수적으로 일어난다. 이때 전자는 빛의 흡수나 발산으로만 전자의 이동이 가능하므로 빛의 광자형태로 에너지 밴드갭 차이를 발산하고 optical device로 사용될 수 있다.

Si 와 같은 indirect 반도체의 경우, bandgap 내에 있는 recombination level을 경유하여 발생하고, 이때 에너지 변화와 동시에 운동량의 변화도 받아야 한다. 이 과정에서 광자보다는 격자의 열로서 에너지를 방출하게 된다.

16. p-n junction diode의 동작

bias가 전혀 없는 평형상태에서 junction 내부에는 이미 W영역에서 공간전하에 의해 내부 전기장은 형성되어 있으나, 캐리어의 diffusion과 drift의 양은 서로 상쇄되기 때문에 실질적인 전류의 흐름은 없다.

Forward bias가 걸리면 potential barrier는 V0-Vf만큼 낮아져 더 많은 캐리어가 확산할 수 있어서 확산전류도 커진다. Reverse bias가 걸리면 potential barrier는 V0+Vr만큼 높아져서 다수캐리어가 확산할 수 없어서 확산전류도 무시할 수 있다. 하지만 캐리어의 drift는 bias에 관계없이 W영역의 전계에 의하여 장벽을 쓸려 내려가면서 drift 전류 성분이 생기게 된다.

17. Depletion Region 이란?

p-n junction의 접합부에서 n-type에서 p-type으로 전자가 확산되고 반대방향으로 hole이 확산되면서, 이 부근에 각각의 캐리어가 거의 공핍되므로 depletion region이라고 부른다. 각각의 캐리어가 확산되면서 뒤에 uncompensated된 도너이온과 억센터 이온을 뒤에 남기므로 n-type에는 양의 공간전하가 p-type에는 음의 공간전하가 형성되므로 space charge region 이라고도 부른다.

18. step junction과 linearly graded junction profile 비교

합금형 junction과 여러 가지 에피텍셜 구조는 step juntion으로 표현 가능하지만, 불순물이 시료 속으로 넓게 퍼져 있는 경우 graded junction 이룰 수 있다. 이를 선형적으로 근사시키면 Nd-Na=Gx와 같은 식으로 나타내어 불순물의 분포를 나타낼 수 있다.

(이 부분은 그래프를 그려서 설명해야 할 것 같습니다.)

19. Built in Voltage란?

Junction 부근에서 W를 가로질러 E(x)=-dV(x)/dx의 경사도가 생긴다. 이 때 중성의 n타입 물질에서 일정한 전위 Vn, p타입 물질에서 일정한 전위 Vp가 있어 두 영역 사이에 전위차 V0가 발생한다. 이 때 Vo를 Built in Voltage라고 하는데 junction에서 평형이 유지되는데 필요한 양이다.

20. diode와 tr의 I-V 특성 곡선

P-N Junction에서 실질적인 전류는 평형상태에서 0이다. Reverse bias에서 확산성분은 무시할 수 있고, n->p의 생성전류뿐이다. Forward bias에서는 캐리어가 확산할 수 있는 확률을 exp(qVf/KT)만큼 증가시킨다. 따라서 전류는 Forward bias와 더불어 지수함수적으로 증가한다.

Transistor에서는

21. Early Effect(Base Width Modulation)

베이스영역이 저농도로 도핑이 되어 있다면 역방향으로 바이어스 된 컬렉터 접합의 W영역은 현저하게 n형의 베이스영역으로 확대될 수 있다. 컬렉터 전압이 증가됨에 따라 이 공간전하층은 베이스의 금속학적 폭 Lb를 더욱 점유하며 그 결과로 유효베이스폭 Wb는 감소한다. 이 효과를 Early Effect(Base Width Modulation)라고 한다.

22. Shottkey(diode) & Ohmic Contact 비교

음전하를 금속 표면 근처에 가져오면 양의 전하가 금속에 유기되고, 이 과정에서 실질적 일함수는 약간 감소된다. 이와 같은 전위장벽의 저하를 Shottkey effect한다. Shottkey barrier diode는 정류성을 이루어, 순방향으로는 전류의 흐름이 쉬우며 역방향으로는 적은 전류를 갖게 된다. 또 순방향 전류는 반도체에서 금속으로의 다수캐리어 주입에 의한 것이다.

Ohmic Contact에서는 Junction 부위에서 최소의 저항을 가지며 신호를 정류시키려는 경향이 전혀 없다. Shottkey barrier diode와는 다르게 평형상태에서 Fermi level을 일치시키는 데 필요한 전위차는 반도체에 다수캐리어의 축적을 요구하게 되므로, 이들 경우에는 반도체에 W영역이 생기지 않는다.

23. doping concentration이 감소하면 VBR이 증가하는 이유

고농도의 도핑이 이루어진 Junction에서는 Reverse bias된 경우 낮은 전압에서 Energy band가 엇갈리게 되고, 이에 따라 Tunneling 현상이 일어나 역전류 현상이 발생한다.(Zener effect) 저농도 도핑의 경우 전자의 터널링 현상은 무시할 수 있으며, 대신 충돌 이온화 효과에 의한 Avalanche effect가 일어난다. 이와 같은 2차 EHP생성의 확률은 각각의 소수캐리어의 농도에 따라 결정되는데, 따라서 저농도 도핑일수록 그 확률은 낮아지므로, breakdown이 발생하기 어려워진다.

24. Eg가 증가하면 VBR이 증가 하는 이유

VBR은 이온화 충돌에 의한 EHP생성시 Eg가 클수록 더 많은 에너지가 필요하므로 Eg가 증가하면 VBR이 증가하게 된다.

25. emitter efficiency, base transport factor, current gain 이란

base transport factor : P-N-P 형 트랜지스터의 경우 iC=BiEp에서 B는 베이스를 넘어서 컬렉터로 가는 injection 된 hole의 성분이고, base transport factor라고 한다.

emitter efficiency : 총 이미터전류 IE 중에서 hole의 성분 iEp의 크기를 말한다.

효율적인 트랜지스터가 되기 위해서 emitter efficiency와 base transport factor가 최대한 1에 가까운 것이 좋다.

이 두 factor의 곱을 current transfer ratio라고 한다.

26. n-channel MOSFET의 동작 mechanism

전압을 게이트에 인가하면 음의 전하가 게이트 금속에 걸리게 되고, 이에 대응하여 그 밑의 Si에 depletion region과 이동성 hole로 인해 음의 전하가 유기 된다. 이들 hole들은 FET의 채널을 형성하며 드레인에서 소스로 전류를 흐르게 한다.

27. CMOS, BJT 동작 원리

CMOS : n-type channel 과 p-type channel의 MOS 트랜지스터를 결합시킨 것이다. n-type channel transistor는 음의 threshold volatge 를 갖고 p-type channel transistor는 양의 threshold volatge 를 같는다.

따라서 입력전압이 0일 때, n-type channel 소자의 게이트 전압은 0V가 되지만, p-type channel 소자에서는 음의 값을 갖는다. 따라서 p-type channel 소자는 on상태, n-type channel 소자에서는 off 상태가 된다.

반면에 양의 전압이 인가되면 n-type channel에서 on, p-type channel에서 off 상태가 된다. 따라서 이 회로는 inverter로 사용될 수 있다.

BJT : 예를 들어 P-N-P형 BJT에서 hole을 base로 injection 하는 영역을 emitter라고 하며, forward bias에 의해 hole이 emitter에서 베이스로 확산해 들어간다. 이 hole들은 Reverse bias에 의해 base로부터 collector로 drift하게 된다. 이 때 base영역에서 재결합으로 인해 소실된 전자와 emitter로 drift해 소실된 전자를 base전류로서 공급하게 된다. 이 과정을 통해 베이스 전류로 컬렉터 전류를 제어할 수 있다.

28. Short Channel Effect와 방지 방법

MOSFET에서 소자가 매우 작아짐에 따라 채널의 길이 짧아지고 이에 따라 drain과 source 가 가지고 있는 전하와 gate의 전하가 전기적으로 공유하게 된다. 소자가 작아질수록 공유되는 전하의 비율이 커지게 되고, Threshold Voltage가 하락하는 roll-off(하락)하는 현상을 보이게 된다.

29. Body Effect

소스 “S”와 Substrate “B”간에 전압을 인가할 수 있는데, S와 B사이에 Reverse bias를 걸어주면 n-type channel 에서 Vb 는 음이기 때문에 Threshold Voltage는 증가 되어야 한다(W영역은 확장하고, inversion 상태를 얻기 위해). Vb 더 큰 음일수록 threshold volatge는 더욱 더 양의 값이 된다.

30. Channel Length Modulation

DIBL 효과에서 드레인 전류는 채널길이에 반비례하므로, 채널길이 변화는 드레인 바이어스에 비례한다고 가정 할 경우, ∆L/L=λVD 로 표현할 수 있고, 여기서 λ를 Channel Length Modulation parameter라고 한다.

31. DIBL(Drain-induced Barrier Lowering) Effect

짧은 채널길이를 갖는 MOSFET이 적당히 스케일링 되지 않고, 소스/드레인 Junction이 너무 깊으면서 채널 도핑이 너무 낮을 경우 발생한다. 채널길이가 짧아짐에 따라 드레인 바이어스가 증가하고, 드레인에서의 Conduct band가 낮아진다. 이로인해 소스와 드레인 사이에서 punch-through나 breakdown을 가져오고 gate가 제어를 상실하게 된다. 이를 방지하기 위해서 채널길이가 짧아질수록 충분히 얇게 만들어야 하고, 채널 도핑을 충분히 크게 해서 punch-through를 방지한다.

32. Subthreshold Conduction Effect

실제로는 Threshold Voltage 아래에서도 여전히 약간의 Drain Conduction 이 존재하는데 이를 Subthreshold Conduction Effect라고 한다. 이러한 전류는 flatband와 threshold voltage 사이에 있는 채널에서의 weak inversion 에 의해 일어난다. 그리고 이는 소스에서 드레인으로의 확산전류를 유발한다.

33. Hot Carrier Effect

하나의 전자가 채널을 따라 Source에서 Drain으로 이동할 때, pinchoff 영역에서 Kinetic 에너지를 얻어서 Hot Carrier가 된다. 이렇게 에너지를 얻게 전자는 커다란 Mobiliy를 얻게 되어, Si-H결합을 파괴하여 Threshold Voltage를 높이고, 전달 컨덕턴스를 낮추는 결과를 나타낸다.

34. LDD(Lightly Doped Drain) 공정

Hot Carrier Effect에 의해 발생한 Threshold Voltage를 높이고, 전달 컨덕턴스를 낮추는 문제를 해결하기 위해 사용하는 방법이다. 소스/드레인에서 도핑농도를 감소시킴으로써 Reverse bias가 걸린 Drain Channel Junction에서 depletion width는 증가되고 전계는 감소시킬 수가 있다.

35. Narrow Channel Effect

MOSFET에서 채널폭 Z가 좁아짐에 따라 Threshold Voltage가 증가한다. Short Channel Effect와는 다르게 소스와 드레인 사이의 전하공유 때문에 일어나게 된다.

36. Flat Band Voltage 와 Vth의 관계(Modified Work Function)

실제 반도체에서는 도핑농도에 따라 Work Function의 차가 달라지고, insulator 또는 interface에서의 전하에 의해 사실상 외부전압이 전혀 없어도 에너지 밴드가 flat하지가 않다. 따라서 flat band를 만들기 위해서 Threshold Voltage Equation을 추가해야 한다. 이 방정식은 flat band 상태를 고려한 후에, depletion 영역의 전하량과 inversion 영역을 유기시키는 항을 포함한다(n-type channel의 경우 이 두 항은 양의 값이고, p-type channel 경우 음의 값을 갖는다).

37. Ampere’s law

전류에 의해 형성된 자기장에서 단위자극이 움직일 때 필요한 일의 양은 단위자극의 경로를 통과하는 전류의 총합에 비례한다. 이 때 자기장의 방향은 오른손의 법칙을 통해 쉽게 구할 수 있다

38. Gauss’s law

전기장과 전하 사이의 관계를 나타낸 법칙이다. 전기장을 둘러싼 폐곡면을 뚫고 폐곡면에 대해 수직방향으로 진행하는 전기장의 흐름은 전체 전하량과 비례한다는 법칙이다.

39. Faraday’s law

유도기전력의 크기는 코일을 관통하는 자속(자기력선속)의 시간적 변화율과 코일의 감은 횟수에 비례한다는 전자기유도법칙이다. 기전력의 방향을 정하는 렌츠의 법칙과 함께 전자기유도가 일어나는 방식을 나타낸다.

40. Ohm’s law

전류의 세기는 두 점 사이의 전위차(電位差)에 비례하고, 전기저항에 반비례한다는 법칙.

41. Continuity Equation

질량 보존의 법칙에 의하여 흐름이 언제든지 연속성을 띠는 것을 나타내는 방정식.

42. Poisson Equation

확률변수 X가 이산형(離散型)으로서 0,1,2,…인 자연수만을 취하고 어떤 값 k를 취하는 확률이

일 때 X의 분포를 푸아송분포라 한다.

43. Laplace Equation 정의

3차원 공간에서의 스칼라함수 φ(x,y,z)가

을 만족할 때, 이 방정식을 라플라스방정식이라고 한다. 이때, 좌변의 미분연산

을 라플라스연산자라 하고, 보통 △로 표시한다.

출처 : Solid State Electronic Devices, 6th edition, Ben G. Streetman

많은 분들이 희망하시는 회사에 취업에 성공하시길 진심으로 바랍니다. (취뽀!)

그럼 다음에는 더 유용한 반도체 관련 지식으로 돌아오겠습니다!